# **Stereo Digital Volume Control**

## DESCRIPTION

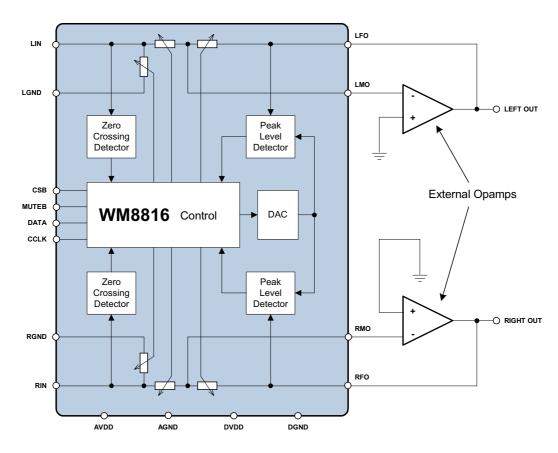

The WM8816 is a highly linear stereo volume control for audio systems. The design is based on resistor chains with external op-amps, which provides flexibility for the supply voltage, signal swing, noise floor and cost optimisation. The gain of each channel can be independently programmed from -111.5dB to +15.5dB through a digital serial control interface.

Audible clicks on gain changes are eliminated by changing gains only when a zero crossing has been detected in the signal. The device also features peak level detection, which can be used for Automatic Gain Control. The WM8816 operates from a single +5V supply and accepts signal input levels up to ±18V.

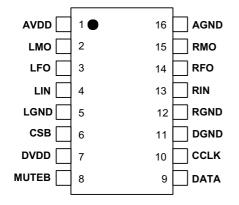

The WM8816 is available in a 16-pin SOIC package. It is guaranteed over a temperature range of  $-20^{\circ}$  to  $+60^{\circ}$ C.

# **FEATURES**

- Gain range from -111.5dB to +15.5dB

- 0.5dB Gain step size

- Total Harmonic Distortion 0.001% (100dB) typical

- Crosstalk -110dB typical

- Input signals up to ±18V

- Zero Detection for Gain Changes

- Hardware and Software Mute

- Power On/Off Transient Suppression

### **APPLICATIONS**

- Audio Amplifiers

- Consumer Audio / Entertainment Systems

- Mixing Desks

- Audio Recording Equipment

# BLOCK DIAGRAM

WOLFSON MICROELECTRONICS plc

www.wolfsonmicro.com

Product Preview, 2004, Rev 1.4

# TABLE OF CONTENTS

| DESCRIPTION                            | 1  |

|----------------------------------------|----|

| FEATURES                               | 1  |

| APPLICATIONS                           | 1  |

| BLOCK DIAGRAM                          | 1  |

| PIN CONFIGURATION                      | 3  |

| ORDERING INFORMATION                   | 3  |

| PIN DESCRIPTION                        | 3  |

| ABSOLUTE MAXIMUM RATINGS               |    |

| RECOMMENDED OPERATING CONDITIONS       | 4  |

| ELECTRICAL CHARACTERISTICS             | 5  |

| CONTROL INTERFACE TIMING DIAGRAM       | 6  |

| REGISTER MAP                           |    |

| PERFORMANCE GRAPHS                     |    |

| RECOMMENDED EXTERNAL COMPONENTS        | 10 |

| RECOMMENDED EXTERNAL COMPONENTS VALUES |    |

| APPLICATION RECOMMENDATIONS            |    |

| PACKAGE DIMENSIONS                     |    |

| IMPORTANT NOTICE                       | -  |

| ADDRESS:                               | 13 |

|                                        |    |

# **PIN CONFIGURATION**

# **ORDERING INFORMATION**

| DEVICE        | TEMPERATURE<br>RANGE | PACKAGE                       | MOISTURE SENSITIVITY<br>LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|---------------|----------------------|-------------------------------|-------------------------------|-------------------------------|

| XWM8816EDW/V  | -20 to +60°C         | 16-pin SOIC (plastic)<br>Wide | MSL3                          | 240°C                         |

| XWM8816GEDW/V | -20 to +60°C         | 16-pin SOIC Wide              | MSL3                          | 260°C                         |

# **PIN DESCRIPTION**

| PIN | NAME  | TYPE             | DESCRIPTION                                      |  |  |  |

|-----|-------|------------------|--------------------------------------------------|--|--|--|

| 1   | AVDD  | Supply           | Supply Voltage for Analogue Circuitry            |  |  |  |

| 2   | LMO   | Analogue Output  | External Op-amp Inverting Input (Left Channel)   |  |  |  |

| 3   | LFO   | Analogue Input   | External Op-amp Feedback Signal (Left Channel)   |  |  |  |

| 4   | LIN   | Analogue Input   | Input Signal (Left Channel)                      |  |  |  |

| 5   | LGND  | Analogue Input   | Input Signal Ground (Left Channel)               |  |  |  |

| 6   | CSB   | Digital Input    | Chip Select (active low)                         |  |  |  |

| 7   | DVDD  | Supply           | Supply Voltage for Digital Circuitry             |  |  |  |

| 8   | MUTEB | Digital Input    | Mute (active low)                                |  |  |  |

| 9   | DATA  | Digital In / Out | Serial Interface Data Input / Output (tri-state) |  |  |  |

| 10  | CCLK  | Digital Input    | Serial Interface Clock                           |  |  |  |

| 11  | DGND  | Supply           | Digital Ground                                   |  |  |  |

| 12  | RGND  | Analogue Input   | Input Signal Ground (Right Channel)              |  |  |  |

| 13  | RIN   | Analogue Input   | Input Signal (Right Channel)                     |  |  |  |

| 14  | RFO   | Analogue Input   | External Op-amp Feedback Signal (Right Channel)  |  |  |  |

| 15  | RMO   | Analogue Output  | External Op-amp Inverting Input (Right Channel)  |  |  |  |

| 16  | AGND  | Supply           | Analogue Ground                                  |  |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore susceptible to damage from excessive static voltages. To optimise the distortion and noise performance of pins 3, 4, 13 and 14, the on-chip ESD protection circuitry has been restricted, and consequently only achieves 300V when characterised to the Human Body Model. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

$$\label{eq:MSL1} \begin{split} \mathsf{MSL1} &= \mathsf{unlimited} \ \text{floor} \ \text{life} \ at <\!\!30^\circ\text{C} \ / \ 85\% \ \text{Relative} \ \text{Humidity}. \ \text{Not normally stored in moisture barrier bag}. \\ \mathsf{MSL2} &= \mathsf{out} \ \text{of} \ \text{bag storage for 1 year} \ at <\!\!30^\circ\text{C} \ / \ 60\% \ \text{Relative} \ \text{Humidity}. \ \text{Supplied in moisture barrier bag}. \\ \mathsf{MSL3} &= \mathsf{out} \ \text{of} \ \text{bag storage for 168 hours} \ at <\!\!30^\circ\text{C} \ / \ 60\% \ \text{Relative} \ \text{Humidity}. \ \text{Supplied in moisture barrier bag}. \\ \end{split}$$

| CONDITION                                            | MIN   | МАХ         |

|------------------------------------------------------|-------|-------------|

| Input signal voltage                                 | -20V  | +20V        |

| Positive supply voltage (AVDD to AGND, DVDD to DGND) | -0.5V | 6V          |

| Input voltage (all other pins)                       | -0.5V | AVDD + 0.5V |

| Operating temperature                                | -40°C | 85°C        |

| Storage temperature                                  | -55°C | 125°C       |

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER               | SYMBOL     | TEST CONDITIONS | MIN | ТҮР | MAX | UNIT |

|-------------------------|------------|-----------------|-----|-----|-----|------|

| Input signal voltage    |            |                 | -18 |     | +18 | V    |

| Positive supply voltage | AVDD, DVDD |                 | 4.5 | 5   | 5.5 | V    |

| Negative supply voltage | AGND, DGND |                 |     | 0   |     | V    |

| Input signal grounds    | LGND, RGND |                 |     | 0   |     | V    |

| Operating temperature   |            |                 | -20 | 60  | 60  | °C   |

# **ELECTRICAL CHARACTERISTICS**

### TEST CONDITIONS

AVDD=5.0V, AGND = 0V,  $T_A = 25^{\circ}$ C, unless otherwise stated.

| PARAMETER                                                           | SYMBOL             | TEST CONDITIONS                                                       | MIN       | TYP   | MAX      | UNIT  |

|---------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------|-----------|-------|----------|-------|

| Analogue Inputs / Outputs                                           |                    |                                                                       |           |       |          |       |

| Input resistance                                                    | R <sub>IN</sub>    | For any gain                                                          | 7         | 10    |          | kΩ    |

| Input capacitance                                                   | CIN                | For any gain                                                          |           | 2     |          | pF    |

|                                                                     |                    | Op-amp gain = -15.5                                                   |           | 0.8   |          | mV    |

| Input offset voltage (note 1)                                       | Voffset            | Op-amp gain = 1                                                       |           | 3     |          | mV    |

|                                                                     |                    | Op-amp gain = 15.5                                                    |           | 12    |          | mV    |

| Supply current                                                      | I <sub>DD</sub>    | From AVDD / AGND                                                      |           | 2.5   | 5        | mA    |

| Power supply rejection ratio<br>(Note 2)                            | PSRR               | From AVDD                                                             |           | 80    |          | dB    |

| Gain Control                                                        |                    |                                                                       |           |       |          |       |

| Gain range                                                          | G                  |                                                                       | -111.5    |       | +15.5    | dB    |

| Gain step size                                                      | D                  |                                                                       |           | 0.5   |          | dB    |

| Gain error (Note 2)                                                 | DE                 | Lowest gains<br>guaranteed by<br>design, not tested in<br>production. |           |       | 0.5      | dB    |

| Gain match error (Note 2)                                           | ME                 | Between channels                                                      |           |       | 0.2      | dB    |

| Mute attenuation                                                    | MATT               |                                                                       | 113       |       |          | dB    |

| Audio Performance                                                   |                    | •                                                                     | ı — I     |       |          |       |

| Noise (Note 2)                                                      |                    | Gain = 0dB                                                            |           |       | 13       |       |

| $V_{IN} = 0V, V_{OUT}$ with OP275,                                  | N                  | Gain = -60dB                                                          |           | 4     |          | μVrms |

| A-weighed                                                           |                    | Gain = mute                                                           |           | 2.5   |          |       |

| Total Harmonic Distortion plus                                      |                    | V <sub>IN</sub> = 1Vrms, gain=0dB,                                    |           |       |          |       |

| Noise                                                               | THD+N              | V <sub>OUT</sub> with OP275,                                          |           | 0.001 |          | %     |

|                                                                     |                    | DC to 20 kHz                                                          |           | (100) |          | (dB)  |

| Dynamic Range (Note 2)                                              | DNR                |                                                                       | 120       | 130   |          | dB    |

| Crosstalk (Note 2)                                                  | CR                 | Between channels,                                                     | -100      | -110  |          | dB    |

|                                                                     |                    | gain=0dB, f <sub>IN</sub> =1kHz                                       |           |       |          |       |

| Digital Inputs / Outputs                                            |                    |                                                                       |           |       |          |       |

| Input low voltage                                                   | VIL                | All digital inputs                                                    |           |       | 0.3 DVDD | V     |

| Input high voltage                                                  | VIH                | All digital inputs                                                    | 0.7 DVDD  |       |          | V     |

| Output low voltage                                                  | Vol                | I <sub>Load</sub> = 2mA                                               |           |       | 0.4      | V     |

| Output high voltage                                                 | Vон                | I <sub>Load</sub> = 2mA                                               | DVDD -0.4 |       |          | V     |

| Control Interface Timing                                            |                    |                                                                       |           |       |          |       |

| Clock Frequency                                                     | f <sub>CCLK</sub>  |                                                                       |           |       | 1        | MHz   |

| Period of CCLK high                                                 | t <sub>WHC</sub>   | V <sub>IH</sub> to V <sub>IH</sub>                                    | 500       |       |          | ns    |

| Period of CCLK low                                                  | t <sub>WLC</sub>   | V <sub>IL</sub> to V <sub>IL</sub>                                    | 500       |       |          | ns    |

| Rise time of CCLK                                                   | t <sub>RC</sub>    | $V_{IL}$ to $V_{IH}$                                                  |           |       | 100      | ns    |

| Fall time of CCLK                                                   | t <sub>FC</sub>    | V <sub>IH</sub> to V <sub>IL</sub>                                    |           |       | 100      | ns    |

| Hold time, CCLK high to CSB low                                     | t <sub>HCSH</sub>  |                                                                       | 20        |       |          | ns    |

| Setup time, CSB low to CCLK high                                    | t <sub>SSLCH</sub> |                                                                       | 100       |       |          | ns    |

| Setup time, valid DATA to CCLK high                                 | t <sub>SDCH</sub>  |                                                                       | 100       |       |          | ns    |

| Hold time, CCLK high to invalid DATA                                | t <sub>HCHD</sub>  |                                                                       | 100       |       |          | ns    |

| Setup time, CCLK low to valid DATA                                  | t <sub>DCLD</sub>  | Load = 100pF                                                          |           |       | 200      | ns    |

| Hold time, CSB high or 16 <sup>th</sup><br>CCLK low to invalid DATA | t <sub>DSZ</sub>   | Load = 3.3kΩ                                                          | 20        |       | 200      | ns    |

PP Rev 1.4 March 2004

### TEST CONDITIONS

AVDD=5.0V, AGND = 0V,  $T_A = 25^{\circ}$ C, unless otherwise stated.

| PARAMETER                                            | SYMBOL             | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |  |  |

|------------------------------------------------------|--------------------|-----------------|-----|-----|-----|------|--|--|--|

| Hold time, 16 <sup>th</sup> CCLK high to<br>CSB high | t <sub>HLCHS</sub> |                 | 200 |     |     | ns   |  |  |  |

| Setup time, CSB high to CCLK high                    | t <sub>sshch</sub> |                 | 200 |     |     | ns   |  |  |  |

Note:

1. External MC33078 op-amp. Will vary depending on op-amp input bias current and input offset voltage.

2. Guaranteed by design.

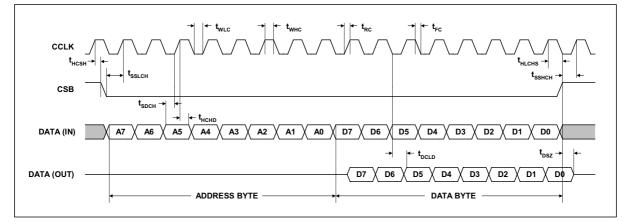

### CONTROL INTERFACE TIMING DIAGRAM

Figure 1 Control Interface Timing Diagram

### **DEVICE DESCRIPTION**

The WM8816 is a stereo digital volume control designed for audio systems. The levels of the left and right analogue channels can be programmed independently through the serial interface. The resistor values in the internal resistor chains are decoded to 0.5 dB resolution with multiplexers, giving a gain range of -111.5 to +15.5 dB. The code for -112 dB activates mute for maximum attenuation.

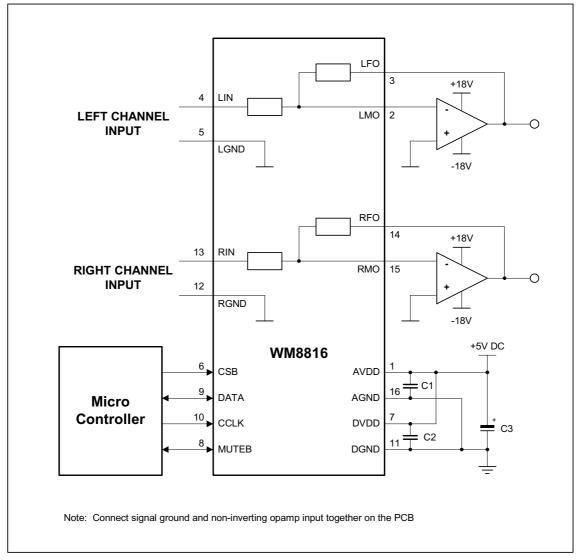

The WM8816 has two constant impedance signal inputs. The left channel input is between LIN and LGND, and the right channel between RIN and RGND. The output pins LFO, LMO (left) and RFO, RMO (right) are designed to interface directly to two external op-amps, which produce the volume controlled output signals. This provides flexibility for the supply voltage and signal swing; while the WM8816 runs at 5V, the output signal swing depends solely on the op-amp supply.

#### INTERFACES

Control information is written into or read back from the internal register via the serial control port. This port consists of a bi-directional data pin (DATA), an active low chip select pin (CSB) and the control clock (CCLK). Control data is shifted into the serial input register on the rising edges of CCLK pulses, while CSB is low. All control instructions require two bytes of data. The first byte contains a 4-bit register address and a read/write bit, and the second byte is the control word. CSB must return to high at the end of each word. When reading from the control registers, data is shifted out on the falling edges of CCLK.

When CSB is high, the DATA pin is in a high impedance state. In a multi-channel system, the same DATA and CCLK lines can thus be connected to several WM8816 volume controllers, and each device can be independently addressed by pulling its CSB pin low.

#### **OPERATING MODES**

When power is first applied, a power-on reset initialises the control registers and mutes the WM8816. To activate the device, the MUTEB pin must be high and a non-zero value must be written to the gain register. After that the device can be muted again either by pulling the MUTEB pin low or by writing zero (00hex) to the gain register.

#### CHANGING THE GAIN OF THE CHANNEL

The WM8816 has two gain registers for the left and right channels respectively. There is also an alias register address to update both gain registers simultaneously. When a new gain value is written into a gain register the WM8816 will wait until the next falling edge zero crossing in the input signal before changing the gain. This ensures that no audible click is produced at the output. If there are no zero crossings in the signal after 23ms internal delay generators change the gain regardless, right channel followed by the left channel. If both gain registers are changed simultaneously, the gain is changed first on the right and then the left channel.

**Note:** The block diagrams in this datasheet only show a representation of the feedback resistor paths and should be thought of as the exact internal device structure. As the internal structure is different, it is not possible to correlate the measured impedance between input and output, and the actual gain attenuation.

#### PEAK LEVEL DETECTION

The WM8816 has an on-chip 8-bit digital-to-analogue converter (DAC) used for monitoring the peak level of the output signal. The DAC input value is programmed via the serial interface. The reference value  $V_{REF}$  is calculated from  $V_{REF} = k/256 \times 18V$ , where k is the DAC input code. When a positive peak signal level exceeds this value, the peak detector sets Bit 1 (for the left channel) or Bit 0 (right channel) of the status register. These bits remain set until the status register is read.

# **REGISTER MAP**

| REGISTER                 |   |   | ADD | RESS | BYTE | BITS |   |   | DATA BYTE                    |                    |  |

|--------------------------|---|---|-----|------|------|------|---|---|------------------------------|--------------------|--|

|                          | 7 | 6 | 5   | 4    | 3    | 2    | 1 | 0 | MSBLSB                       | Function           |  |

| Peak Detector Status     | Х | 1 | 0   | 1    | 1    | R/W  | Х | Х | Output code                  |                    |  |

| R4                       |   |   |     |      |      |      |   |   | 00000000                     | No overload        |  |

|                          |   |   |     |      |      |      |   |   | 0000001                      | Right overload     |  |

|                          |   |   |     |      |      |      |   |   | 0000010                      | Left overload      |  |

|                          |   |   |     |      |      |      |   |   | 00000011                     | Both overload      |  |

| Peak Detector            | Х | 1 | 1   | 0    | 0    | R/W  | Х | Х | Input code                   | DAC output         |  |

| Reference                |   |   |     |      |      |      |   |   | 11111111                     | 255/256 × 18V      |  |

| R3                       |   |   |     |      |      |      |   |   | 11111110                     | 254/256 × 18V      |  |

|                          |   |   |     |      |      |      |   |   | 11111101                     | 253/256 × 18V      |  |

|                          |   |   |     |      |      |      |   |   | :                            | :                  |  |

|                          |   |   |     |      |      |      |   |   | 0000010                      | 2/256 × 18V        |  |

|                          |   |   |     |      |      |      |   |   | 0000001                      | $1/256 \times 18V$ |  |

|                          |   |   |     |      |      |      |   |   | 00000000                     | AGND               |  |

| Left Channel Gain        | Х | 1 | 1   | 0    | 1    | R/W  | Х | Х | Input code                   | Gain dB            |  |

| R2                       |   |   |     |      |      |      |   |   | 11111111                     | +15.5              |  |

|                          |   |   |     |      |      |      |   |   | 11111110                     | +15.0              |  |

|                          |   |   |     |      |      |      |   |   | 11111101                     | +14.5              |  |

|                          |   |   |     |      |      |      |   |   | :                            | :                  |  |

|                          |   |   |     |      |      |      |   |   | 11100000                     | 0.0                |  |

|                          |   |   |     |      |      |      |   |   | 0000010                      | -111.0             |  |

|                          |   |   |     |      |      |      |   |   | 0000001                      | -111.5             |  |

|                          |   |   |     |      |      |      |   |   | 00000000                     | mute               |  |

| Right Channel Gain       | Х | 1 | 1   | 1    | 0    | R/W  | Х | Х | Input code                   | Gain dB            |  |

| R1                       |   |   |     |      |      |      |   |   | 11111111                     | +15.5              |  |

|                          |   |   |     |      |      |      |   |   | 11111110                     | +15.0              |  |

|                          |   |   |     |      |      |      |   |   | 11111101                     | +14.5              |  |

|                          |   |   |     |      |      |      |   |   | :                            | :                  |  |

|                          |   |   |     |      |      |      |   |   | 11100000                     | 0.0                |  |

|                          |   |   |     |      |      |      |   |   | 0000010                      | -111.0             |  |

|                          |   |   |     |      |      |      |   |   | 0000001                      | -111.5             |  |

|                          |   |   |     |      |      |      |   |   | 0000000                      | mute               |  |

| Both Channel Gains<br>R5 | х | 1 | 0   | 0    | 1    | W    | х | х | Write to both gain registers |                    |  |

#### Table 1 Register Map Description

#### Notes:

1. Address bit 2 is the read / write bit (1 for read, 0 for write).

2. X represents 'do not care' entries. Set to 1 for minimum power consumption.

3. All registers are set to their default value (all zeros) during power-on reset, except R3 which is set to 255.

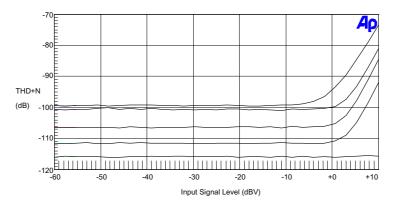

# **PERFORMANCE GRAPHS**

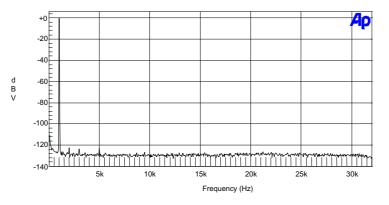

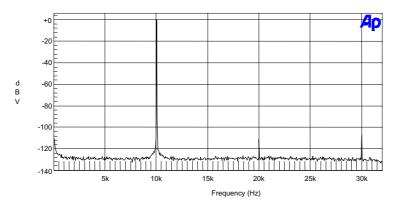

Figure 2 THD + Noise versus input level at gains of +6dB, 0dB, -6dB, -12dB and mute

Figure 3 FFT of output signal with 1kHz, 1Vrms sine wave input

Figure 4 FFT of output signal with 10kHz, 1Vrms sine wave input

# **RECOMMENDED EXTERNAL COMPONENTS**

Figure 5 Typical Application.

# **RECOMMENDED EXTERNAL COMPONENTS VALUES**

| COMPONENT<br>REFERENCE | SUGGESTED<br>VALUE | DESCRIPTION                |

|------------------------|--------------------|----------------------------|

| C1                     | 220nF              | Analogue Supply Decoupling |

| C2                     | 220nF              | Digital Supply Decoupling  |

| C3                     | 10µF               | General Supply Decoupling  |

Table 2 Recommended External Components Values

#### **APPLICATION RECOMMENDATIONS**

- For best audio performance, all digital activities should be minimised during analogue signal processing. Special attention should be paid to power and ground decoupling. Decoupling capacitors should be located as close to the WM8816 as possible. A clean analogue power supply should always be used.

- 2. Damage can be caused to the internal delay generators if AVDD and DVDD supply voltages differ to any degree. The AVDD and DVDD pins must therefore be tied together in all designs.

- During operation of the hardware MUTEB function between setting mute and then un-mute, the device may either not un-mute or the gain setting after un-mute will be incorrect. It is advised to re-write the gain settings immediately following hardware un-mute to guarantee faultless operation.

- 4. Voltage greater than 500mV on the digital pins while the device is powered down may prevent successful POR of the device when power is re-applied. It is preferable that all digital pins are pulled low during power up or alternatively ensure that there are no residual voltages held on the digital pins during power down.

- 5. The WM8816 output offset voltage can vary dependent upon the op-amp used usually with the largest level of offset voltage occurring at +15.5dB gain. Output offset voltage has linear relationship on input bias current and offset voltage amplitudes. Using differing op-amp types causes a large variation in offset voltage. Below is a list of recommended op-amps which are found to give the least offset issues when used with the WM8816. Channel matching is also important factor and not necessarily only the absolute offset value.

| DEVICE    | MANUFACTURER   | OFFSET<br>IN MV |

|-----------|----------------|-----------------|

| OP275     | Analog Devices | 8.55            |

| MC33078/9 | On-Semi/ST     | 28.4            |

| AD8610    | Analog Devices | 1.49            |

| LT1793    | Linear         | 18.5            |

| OP1177    | Analog Devices | 0.505           |

| OP277     | BurrBrown      | 0.228           |

**Table 3 Recommended Op-amps**

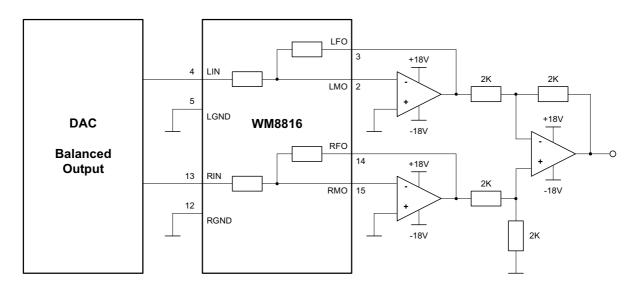

Figure 6 Configuration for Double Balanced Output (One Channel)

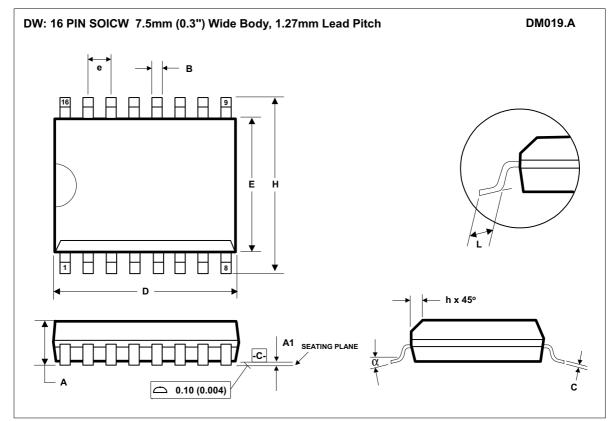

# PACKAGE DIMENSIONS

| Symbols               |       | nsions<br>m) | Dimensions<br>(Inches) |        |  |  |

|-----------------------|-------|--------------|------------------------|--------|--|--|

|                       | MIN   | MAX          | MAX MIN                |        |  |  |

| Α                     | 2.35  | 2.65         | 0.0926                 | 0.1043 |  |  |

| <b>A</b> <sub>1</sub> | 0.10  | 0.30         | 0.0040                 | 0.0118 |  |  |

| В                     | 0.33  | 0.51         | 0.0130                 | 0.0200 |  |  |

| С                     | 0.23  | 0.32         | 0.0091                 | 0.0125 |  |  |

| D                     | 10.10 | 10.50        | 0.3465                 | 0.3622 |  |  |

| е                     | 1.27  | BSC          | 0.0500 BSC             |        |  |  |

| E                     | 7.40  | 7.60         | 0.2914                 | 0.2992 |  |  |

| h                     | 0.25  | 0.75         | 0.0100                 | 0.0290 |  |  |

| Н                     | 10.00 | 10.65        | 0.3940                 | 0.4190 |  |  |

| L                     | 0.40  | 1.27         | 0.0160 0.050           |        |  |  |

| α                     | 0°    | 8°           | 0°                     | 8°     |  |  |

|                       |       | -            | -                      | • •    |  |  |

| REF:                  |       | JEDEC.9      | 5, MS-013              |        |  |  |

NOTES: A. ALL LINEAR DIMENSIONS ARE IN MILLIMETERS (INCHES). B. THIS DRAWING IS SUBJECT TO CHANGE WITHOUT NOTICE. C. BOOY DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSION, NOT TO EXCEED 0.25MM (0.010IN). D. MEETS JEDEC.95 MS-013, VARIATION = AA. REFER TO THIS SPECIFICATION FOR FURTHER DETAILS.

Wolfson Microelectronics plc (WM) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current. All products are sold subject to the WM terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

WM warrants performance of its products to the specifications applicable at the time of sale in accordance with WM's standard warranty. Testing and other quality control techniques are utilised to the extent WM deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

In order to minimise risks associated with customer applications, adequate design and operating safeguards must be used by the customer to minimise inherent or procedural hazards. Wolfson products are not authorised for use as critical components in life support devices or systems without the express written approval of an officer of the company. Life support devices or systems are devices or systems that are intended for surgical implant into the body, or support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided, can be reasonably expected to result in a significant injury to the user. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

WM assumes no liability for applications assistance or customer product design. WM does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of WM covering or relating to any combination, machine, or process in which such products or services might be or are used. WM's publication of information regarding any third party's products or services does not constitute WM's approval, license, warranty or endorsement thereof.

Reproduction of information from the WM web site or datasheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated WM product or service, is an unfair and deceptive business practice, and WM is not responsible nor liable for any such use.

Resale of WM's products or services with <u>statements different from or beyond the parameters</u> stated by WM for that product or service voids all express and any implied warranties for the associated WM product or service, is an unfair and deceptive business practice, and WM is not responsible nor liable for any such use.

### ADDRESS:

Wolfson Microelectronics plc 26 Westfield Road Edinburgh EH11 2QB United Kingdom

Tel :: +44 (0)131 272 7000 Fax :: +44 (0)131 272 7001 Email :: sales@wolfsonmicro.com